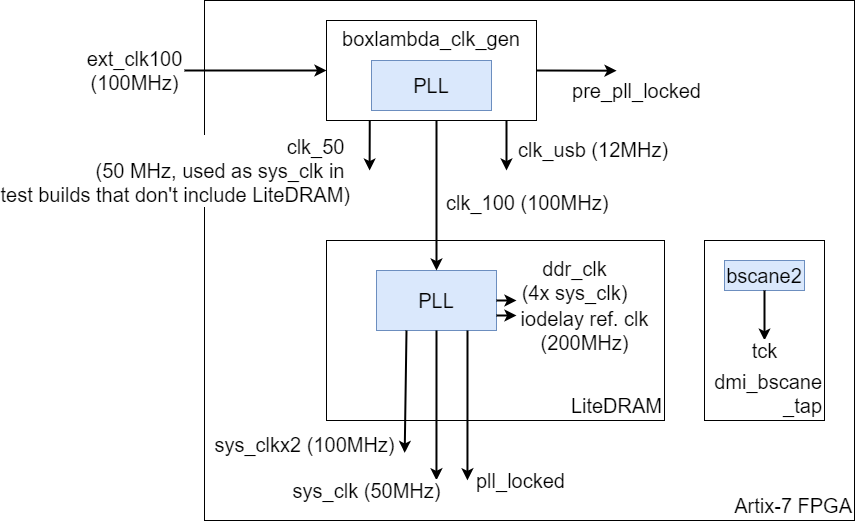

Clocks

BoxLambda's Clocks.

The following clocks are present in the SoC:

- ext_clk_100: 100MHz external clock, input to the LiteDRAM core.

- sys_clk: 50MHz System Clock, generated by the LiteDRAM core, used by rest of SoC (CPU, Interconnect,...).

- sys_clkx2: 100MHz Double Rate System Clock, generated by the LiteRAM core, twice the rate of, and in phase with sys_clk. Sys_clkx2 is used by the PicoRV core.

- ddr_clk: SDRAM DDR PHY clock running at 4xsys_clk, generated by the LiteDRAM core.

- 200MHz reference clock for IODELAYs, generated and used the LiteDRAM core.

- tck: JTAG clock, driven via a BSCANE2 primitive by the FPGA's JTAG chain. The BSCANE2 primitive is instantiated in the dmi_bscane_tap module.

- usb_clk: 12MHz clock for the USB HID Host cores.

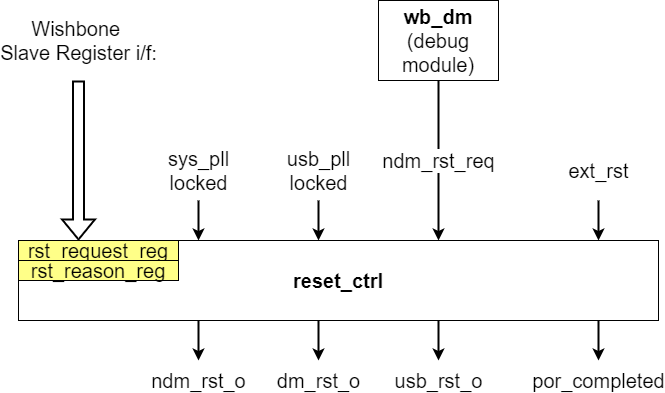

Reset

-

Reset Controller Component in the BoxLambda Directory Tree: boxlambda/gw/components/reset_ctrl

-

Reset Controller Top-Level: gw/components/reset_ctrl/rtl/reset_ctrl.sv

-

Reset Controller HAL: TBD

BoxLambda has the following synchronous Reset Domains:

- dm_reset: Resets the Debug Module Logic in the system clock domain.

- ndm_reset: Resets the Non-Debug Module Logic in the system clock domain.

- usb_reset: Resets the logic in the USB clock domain.

BoxLambda has the following Reset Sources:

- Power-On Reset: Asserted for several clock cycles after Power-On.

- External Reset: Connected to a reset button on the Arty A7 board.

- Non-Debug Module Reset Request: issued by the Debug Module.

- Software Reset: Reset of dm_reset, ndm_reset, or usb_reset domain triggered by software by writing to a reset_ctrl register.

The management of these reset domains and reset sources is organized by a reset_ctrl module.

BoxLambda's Reset Controller.

The reset_ctrl module code is located here:

https://github.com/epsilon537/boxlambda/blob/master/gw/components/reset_ctrl/rtl/reset_ctrl.sv

Reset Controller Registers

Software can trigger resets by writing to the Reset Control Register and retrieve the reason for the most recent reset by reading from the Reset Reason Register:

| Address | Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|---|---|

| 0x10000030 | RESET_CTRL | - | - | - | - | - | USB_RESET | DM_RESET | NDM_RESET |

| 0x10000034 | RESET_REASON | - | - | SW_USB | EXT | NDM | SW_DM | SW_NDM | POR |

The Reset Reason Register's contents are cleared after reading from it (Read-Reset).